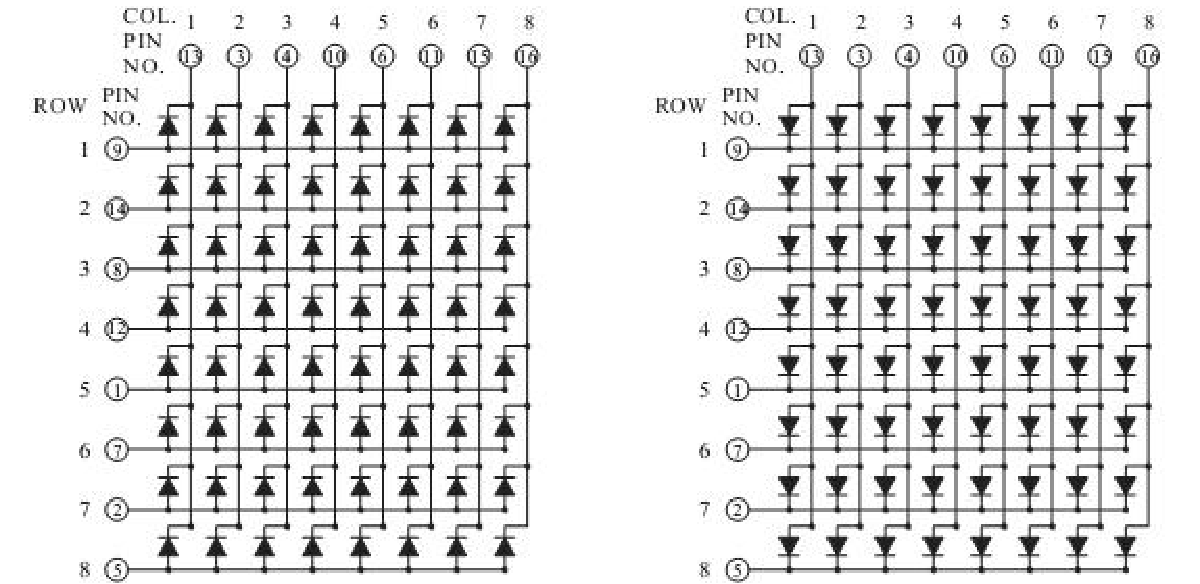

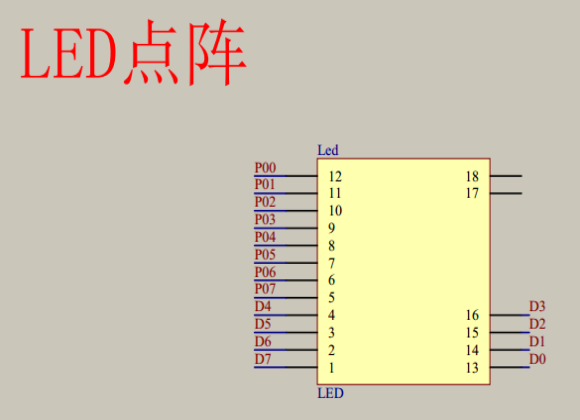

8x8LED

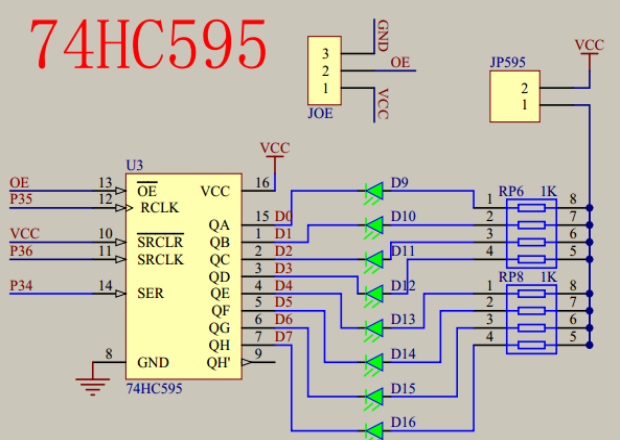

P0口控制列,p3^6,p3^5,p3^4控制行。

中断系统

中断的概念

CPU在处理某一事件A时,发生了另一事件B请求CPU迅速去处理(中断发生); CPU暂时中断当前的工作,转去处理事件B(中断响应和中断服务); 待CPU将事件B处理完毕后,再回到原来事件A被中断的地方继续处理事件A(中断返回),这一过程称为中断 。

引起CPU中断的根源,称为中断源。中断源向CPU提出的中断请求。CPU暂时中断原来的事务A,转去处理事件B。对事件B处理完毕后,再回到原来被中断的地方(即断点),称为中断返回。实现上述中断功能的部件称为中断系统。

随着计算机技术的应用,人们发现中断技术不仅解决了快速主机与慢速I/O设备的数据传送问题,而且还具有如下优点:

分时操作。CPU可以分时为多个I/O设备服务,提高了计算机的利用率;

实时响应。CPU能够及时处理应用系统的随机事件,系统的实时性大大增强;

可靠性高。CPU具有处理设备故障及掉电等突发性事件能力,从而使系统可靠性提高。

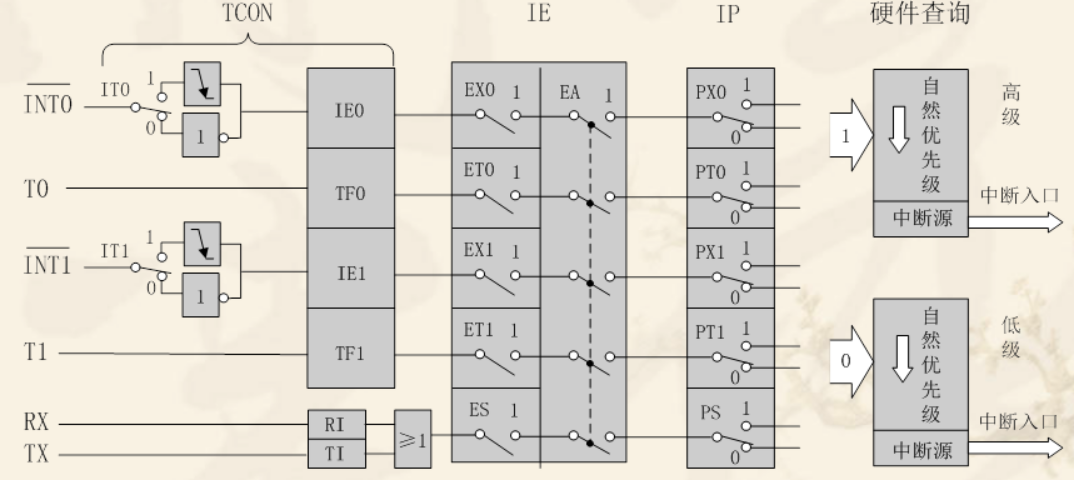

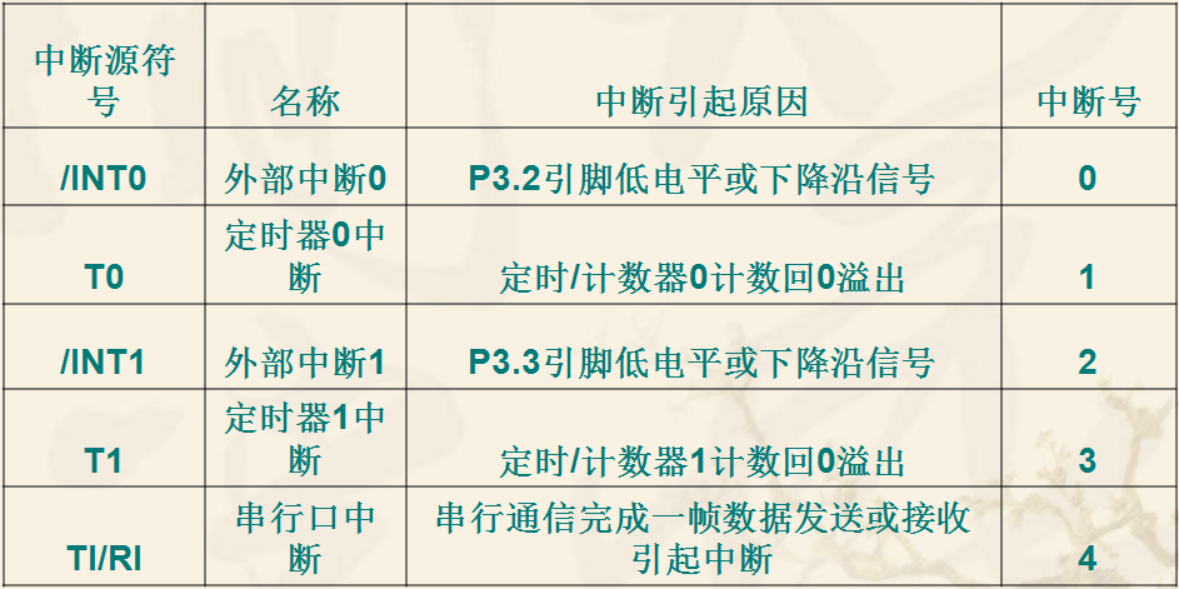

89C51/52的中断系统有5个中断源 ,2个优先级,可实现二级中断嵌套 。

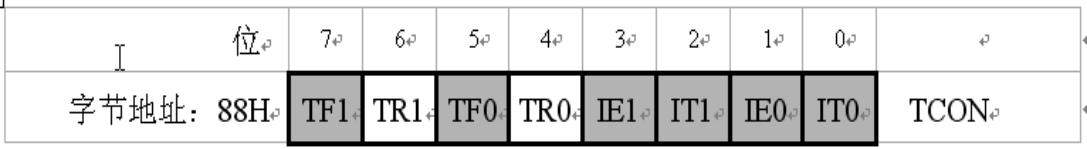

(P3.2)可由IT0(TCON.0)选择其为低电平有效还是下降沿有效。当CPU检测到P3.2引脚上出现有效的中断信号时,中断标志IE0(TCON.1)置1,向CPU申请中断。

(P3.3)可由IT1(TCON.2)选择其为低电平有效还是下降沿有效。当CPU检测到P3.3引脚上出现有效的中断信号时,中断标志IE1(TCON.3)置1,向CPU申请中断。

TF0(TCON.5),片内定时/计数器T0溢出中断请求标志。当定时/计数器T0发生溢出时,置位TF0,并向CPU申请中断。

TF1(TCON.7),片内定时/计数器T1溢出中断请求标志。当定时/计数器T1发生溢出时,置位TF1,并向CPU申请中断。

RI(SCON.0)或TI(SCON.1),串行口中断请求标志。当串行口接收完一帧串行数据时置位RI或当串行口发送完一帧串行数据时置位TI,向CPU申请中断。

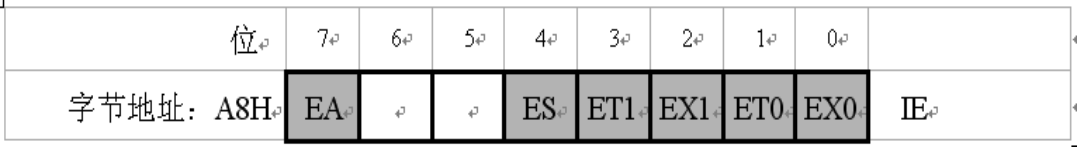

中断允许控制

CPU对中断系统所有中断以及某个中断源的开放和屏蔽是由中断允许寄存器IE控制的。

EX0(IE.0),外部中断0允许位;

ET0(IE.1),定时/计数器T0中断允许位;

EX1(IE.2),外部中断0允许位;

ET1(IE.3),定时/计数器T1中断允许位;

ES(IE.4),串行口中断允许位;

EA (IE.7), CPU中断允许(总允许)位。

中断请求标志

TCON的中断标志

IT0(TCON.0),外部中断0触发方式控制位。 当IT0=0时,为电平触发方式。 当IT0=1时,为边沿触发方式(下降沿有效)。

IE0(TCON.1),外部中断0中断请求标志位。

IT1(TCON.2),外部中断1触发方式控制位。

IE1(TCON.3),外部中断1中断请求标志位。

TF0(TCON.5),定时/计数器T0溢出中断请求标志位。

TF1(TCON.7),定时/计数器T1溢出中断请求标志位。

优先级

中断源

CPU同时接收到几个中断时,首先响应优先级别最高的中断请求。

正在进行的中断过程不能被新的同级或低优先级的中断请求所中断。

正在进行的低优先级中断服务,能被高优先级中断请求所中断。

为了实现上述后两条原则,中断系统内部设有两个用户不能寻址的优先级状态触发器。其中一个置1,表示正在响应高优先级的中断,它将阻断后来所有的中断请求;另一个置1,表示正在响应低优先级中断,它将阻断后来所有的低优先级中断请求。

中断响应条件

中断源有中断请求;

此中断源的中断允许位为1;

CPU开中断(即EA=1)。

以上三条同时满足时,CPU才有可能响应中断。